PCI Expressはコンピュータ バスの重要な部分であり、各デバイスには独自の専用接続があり、以前の PCI よりもはるかに高速です。

PCIeとは

2002年7月23日、Intelは、3GIOを正式にPeripheral Component Interconnect Expressに改名しました。Intelは、バスの重要な分岐点として、業界で人気のあるポイントツーポイントシリアル接続を採用し、シリアル通信システムの標準を改善しました。そのインターフェイスは、バス幅によって異なります。

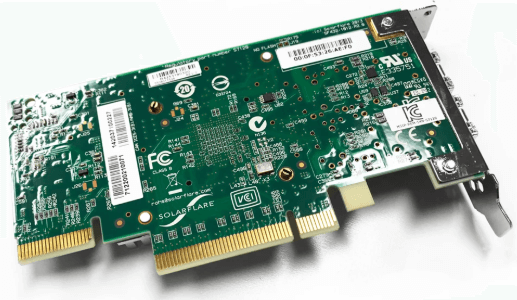

ほとんどのパーソナルコンピューターのグラフィックスカード、SSD、イーサネットハードウェア、Wi-Fi、ハードドライブ接続は、PCIeをマザーボード接続として使用します。

ヒント:SSDまたはハードドライブに変更を加えたい場合は、MiniToolソフトウェアを試してください。

異なるバージョンのPCIe

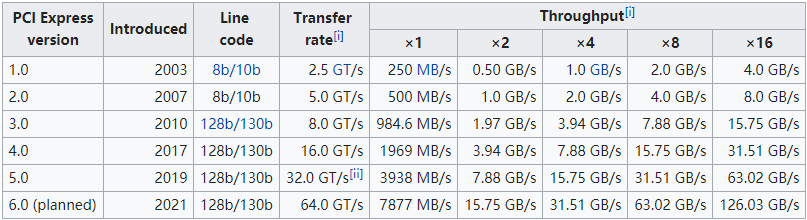

2003年、PCI Expressがリリースされてから、多くの調整と改善が行われ、いくつかのバージョンがリリースされました。

PCI Express 1.0aと1.1

2003年、PCI-SIGはPCIe 1.0aをリリースし、レーンあたりのデータレートは250 MB/sに達し、伝送速度は 2.5GT/sに達しました。2005年に導入されたPCIe 1.1は、データレートを改善することなく、いくつかの改善のみを行いました。

PCI Express 2.0と2.1

2007年、PCI-SIGによって導入されたPCI Express 2.0は、1レーンあたりのデータレートを500MB/sに向上し、32レーンのPCIeコネクタは最大16 GB/sの転送速度に対応しています。

さらに、PCIe 2.0のマザーボードスロットは完全な下位互換性があり、PCIe 2.0カードは基本的に下位互換性があります。PCIe 2.0では、ポイントツーポイントのデータ転送プロトコルを改善しました。5 GT/sのRawデータレートから最大4 Gbit/sのレーンあたりのデータレートを提供できます。

PCIe 2.1は、PCI Express 3.0に実装されるほとんどの管理、サポート、トラブルシューティングシステムをサポートしますが、PCIe 2.1カードは、スロットからの電力が増加するため、1.0/1.1a dの一部の古いマザーボードに対応していません。

PCI Express 3.0と3.1

2010年11月、PCI-SIGは8 GT/sの転送速度を持つPCI Express 3.0を導入しました。PCIe 3.0エンコーディング スキームは、以前の8b/10bからより効率的な128b/130bに変更され、PCIe 2.0の20%の帯域幅オーバーヘッドが1.54%に削減され、その他の仕様は基本的に変更されていません。さらに、PCIe 3.0は下位互換性もサポートします。

PCIe 3.0は、帯域幅のデータスループットが大幅に向上したことに加え、信号速度の高速化とデータ伝送遅延の低減を実現しています。PCIe 3.0は、強化されたシグナリングとデータの整合性も最適化しています。

2014年11月にリリースされたPCIe 3.1は、PCIe 3.0に比べ、電力管理、パフォーマンス、機能が改善されました。

PCI Express 4.0

2017年6月8日にリリースされたPCIe 4.0は、PCIe 3.0の2倍の帯域幅である16 GT/秒のビットレートを提供し、後方互換性と前方互換性を提供し、柔軟性、拡張性、低消費電力を向上させます。

PCI Express 5.0

PCI Express 5.0は、2019年5月29日に正式にリリースされ、帯域幅は32 GT/sに増加しました。16チャネル構成では、各方向で63GB/sが生成されます。

PCI Express 6.0

PCIe 6.0は2021年にリリースされる予定で、帯域幅は64GT/sに増加し、16チャネル構成では各方向に128 GB/sになります。

PCIeの利点

PCIeバスはポイントツーポイントのシリアル接続デバイス接続を採用しており、各PCIeデバイスはそれぞれ独立したデータ接続を持ち、各デバイス間の同時データ転送は互いに影響しません。

PCIeバスは、シリアル接続の機能を利用してデータ転送速度を非常に高い周波数にし、その転送速度はバスのビット幅によって変化します。さらに、PCIeバスは双方向伝送モードをサポートしており、より高い伝送速度と品質を提供します。

PCIeのハードウェアプロトコル

PCIeは、トランザクション層、データリンク層、物理層を組み合わせた階層化されたプロトコルです。

トランザクション層

PCIeでは、スプリットトランザクション方式を採用することで、ターゲット機器が応答データを収集する際に、リンクで他のトラフィックを伝送できます。信頼できるフロー制御を採用しています。

データリンク層

データリンク層は、トランザクション層が生成したパケットをソートし、2つのエンドポイント間でTLPを確実に渡すことができます。LCRCチェックサムの連続性チェックをパスできるAckをAck (コマンド正解応答)と呼びます。チェックをパスしたTLPはNak(応答なし)と呼ばれ、応答しないTLP、タイムアウトを待つTLPは再送信されます。

物理層

物理層は電気仕様と論理仕様に分けられ、論理的仕様はMACとPCSに分けられます。電気レベルでは、各チャネルは2つの単方向差動ペアで構成され、送信と受信で別々の差動ペアを持ち、レーンごとに合計4つのデータラインがあります。

2つのPCIeデバイス間の接続がリンクです。デバイスは2、4、8、12、16、32チャネルリンクのサポートを選択できるため、2つの良好な互換性を実現する方法があります。

PCIeの適用

PCIeは、消費、サーバー、産業用のアプリで使用されています。2005年には、ほぼすべてのパソコンのマザーボードがPCIeを採用しました。2013年、PCIeは新しいシステムのグラフィックスカードのデフォルトインターフェイスとしてAGPに取って代わりました。PCIeは現在、あらゆる種類のネットワークカード、サウンドカード、グラフィックカード、現在のNVMe SSDで使用されています。